|

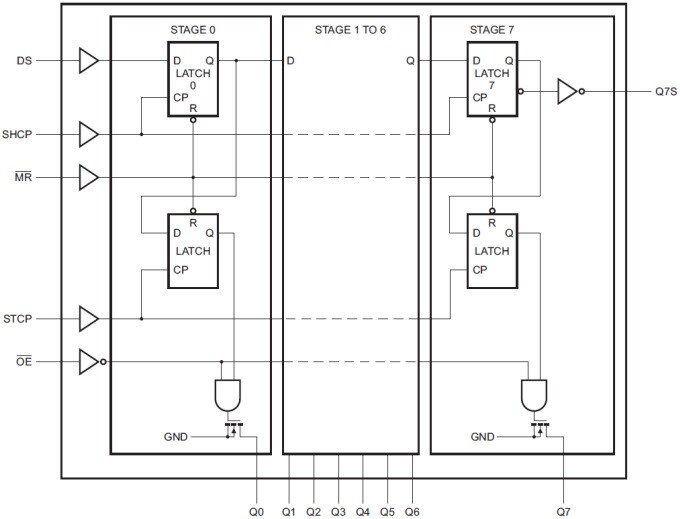

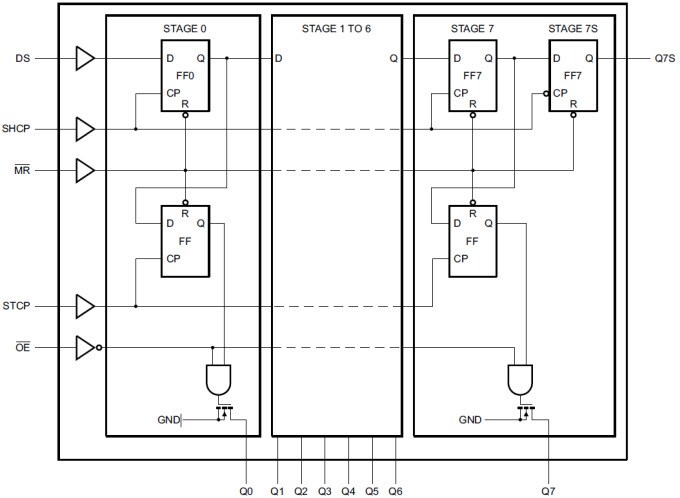

Registro de desplazamiento lógico de alimentación NPIC6C595/596 de NXPEl registro de desplazamiento lógico de alimentación NPIC6C595/596 de NXP es un registro de desplazamiento en serie o no en paralelo con registro de almacenamiento y salidas de drenaje abierto. Tanto el registro de desplazamiento como el de almacenamiento tienen relojes independientes. El dispositivo incluye una entrada en serie (DS) y una salida en serie (Q7S) para permitir la distribución en cascada y una entrada MR de reinicio asíncrono. Un LOW en la entrada MR reinicia tanto el registro de desplazamiento como el de almacenamiento. Los datos se desplazan en las transiciones LOW a HIGH de la entrada SHCP. Los datos del registro de desplazamiento se transfieren al registro de almacenamiento en una transición de LOW a HIGH de la entrada STCP. Si ambos relojes están conectados entre sí, el registro de desplazamiento siempre va un pulso de reloj por delante del registro de almacenamiento. |

|

Características

Aplicaciones

Recursos adicionales

|

| Diagramas lógicos |

|

España

España

Por favor, confirme su moneda:

|

Euros

Envío de pedido gratuito en la mayoría de pedidos superiores a 50 € (EUR) |

|

Dólares estadounidenses

Envío de pedido gratuito en la mayoría de pedidos superiores a $60 (USD) |

Hoja de datos de NPIC6C595

Hoja de datos de NPIC6C595