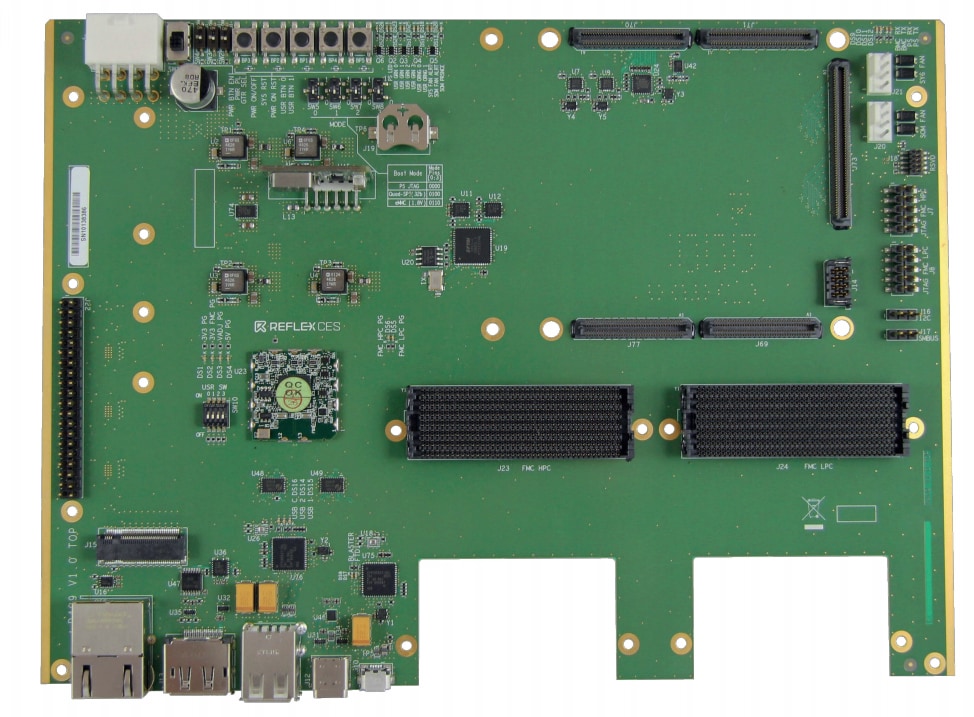

ReFLEX CES Zeus Zynq® UltraScale+™ MPSoC SoM Carrier Board

ReFLEX CES Zeus Zynq® UltraScale+™ MPSoC SoM Carrier Board is based on the Xilinx® UltraScale™ MPSoC architecture. The Zeus Carrier Board integrates a 64-bit quad-core and dual-core Arm® Cortex-R5 based processing system (PS) and Xilinx programmable logic (PL) UltraScale architecture. REFLEX CES has selected the Zynq ultrascale+ MPsoC FPGA for its ever-unmatched performances, as well as for its lower system power architecture. The Zynq Ultrascale+ MPsoC FPGA is more innovative and optimized for differentiation, analytics, and control.Specifications

- Dual FMC+ connectors

- FMC+ HPC: 16 transceivers @12.5Gbps, 58x LVDS, 44x SE

- FMC+ LPC: 16 transceivers @12.5Gbps, 34x LVDS

- PS Interfaces

- 1x GbE, I2C, SPI

- 2x USB2.0 Type-A, USB3.1 Type-C, DP Out

- 43x MIO: 2 x 20 header Raspberry Pi HAT pinout

- M.2 NVMe interface (M.2 NVMe drive not provided)

- Misc.

- RTC battery holder

- On-board E2PROMS (BMC I2C, PS I2C)

- Communication Interfaces

- FPGA= USB to JTAG

- BMC= USB to UART

- PS= USB to UART

- -40°C to +85°C (except RTC battery) Operating temperature

- 170mm x 233.35mm Board dimensions

- Compliance

- Fully compatible with Zeus Zynq® UltraScale+™ module

- RoHS/REACH compliant

- UL certified

- ISO9001 Facility

Applications

- Software-defined radio

- Radar systems

- Electronic warfare

- High precision measurement

Kit Contents

- Carrier board of the Zeus Zynq UltraScale+ MPSoC module

- Power supply and cables (US, UK, EU, JP), micro-USB cable

- Board Support Package (to download from our online technical support):

- Starter Guide, Module and carrier board Reference Manuals

- HDL Test Designs by an interface (Vivado 2020.2 version)

- Linux Kernel & Linaro optimized distribution, U-boot bootloader, test scripts

- Mechanical drawings, assembly files

- Interconnect pinout file

- Carrier board schematics, carrier board design guide

Layout

Block Diagram

Publicado: 2021-09-28

| Actualizado: 2022-03-11